# Low-Noise High-PSRR 100mA LDO Regulator in SC-70 Package

## Technical Data Sheet

**ASI3101**

### **FEATURES**

Low-Noise Low-Drop-Out Regulator with 1.8V/2.5V/3.3V Preset Output

Stable with 0.47 $\mu$ F Ceramic Capacitor for Any Load

High Output Current: 100mA Low Output Noise: 12µVrms

Low Quiescent Current: 90µA (typical) 200mV Dropout at 100mA Load (typical) Only Need Input and Output Capacitors Low Leakage Shutdown Mode (<1µA)

Thermal Protection Shutdown

Short-Circuit Output Limit Protection

Built-in Internal Soft-Start Circuit

## **APPLICATIONS**

Mobile Phones

Wireless LANs

Bluetooth portable devices

USB portable devices

GSM/3G RF Transceiver Modules

PDA, Palm and Notebook Computers

DSC, Handset Camera Module

PCMCIA cards

Personal Portable device

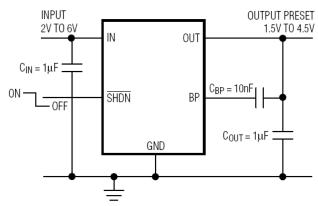

**Typical Application Circuit**

### GENERAL DESCRIPTION

This linear regulator family consists of a series of 100mA ultra-low-noise, low dropout (LDO) linear regulators designed for battery-powered equipments. The regulator achieves a low 200mV dropout at 100mA load current, low output voltage noise of  $12\mu Vrms$  and PSRR of 65dB at 1KHz. The ASI3101 also works with low-ESR ceramic capacitors, reducing the amount of board space necessary for power applications, critical in hand-held devices. The ASI3101 consumes less than  $0.01\mu A$  in shutdown mode.

The other features include high output voltage accuracy, thermal over-temperature and current limiting protection. This LDO product is available in 5-pin tiny SC70 package.

## **ELECTRICAL SPECIFICATIONS**

At  $T_A$  =25°C ,  $V_{IN}$  =(  $V_{OUT}$  +0.5V),  $C_{IN}$  =C  $_{OUT}$  =0.47  $\mu F$  ,  $V_{EN}$  =V  $_{IN}$  , unless otherwise noted.

#### Table 1

| Parameter                   | Conditions                           | Min          | Тур  | Max                  | Unit                 |

|-----------------------------|--------------------------------------|--------------|------|----------------------|----------------------|

| Input Voltage Range         |                                      | 2.0          |      | 5.5                  | V                    |

| Output Voltage              | Metal Mask Programmable              | 1.8          |      | 3.3                  | V                    |

| Output Voltage Accuracy     | lout = 0.1uA to 80mA                 | -1.5         |      | +1.5                 | %                    |

| Output Current Limit        | Shorted-Circuit Output               |              | 150  |                      | mA                   |

| Dropout Voltage             | Vout > 3V, lout = 100mA              | 200          |      | mV                   |                      |

| Dropout Voltage             | 2V < Vout < 3V, lout = 100mA         | 280          |      | mV                   |                      |

| Dropout Voltage             | Vout < 2V, lout = 100mA              | 400          |      | mV                   |                      |

| Ground Current              | lout = 0.05mA                        | 90           |      | mA                   |                      |

| Line Regulation             |                                      |              | 0.1  |                      | %/V                  |

| Load Regulation             |                                      |              | 0.01 |                      | %/mA                 |

| Shut-down Current           |                                      |              | 0.01 |                      | μV                   |

| PSRR                        | f = 100Hz, lout = 1mA                |              | 68   |                      | dB                   |

| PSRR                        | f = 1KHz, lout = 1mA                 | 65           |      | dB                   |                      |

| PSRR                        | f = 10KHz, lout = 1mA                |              | 50   |                      | dB                   |

| Output Noise Voltage        | f = 100Hz to 100KHz, lout = 10mA     | 12           |      | μVrms                |                      |

| Shutdown Exit Delay         | Rload=50ohm                          |              |      | 300                  | μs                   |

| SHDN Logic Low Level        | V <sub>IN</sub> =2.0V to 5.5V        |              |      | 0.5                  | V                    |

| SHDN Logic High Level       | V <sub>IN</sub> =2.0V to 5.5V        | 5.5V 1.5 Vin |      | V                    |                      |

| SHDN Input Bias Current     | V <sub>IN</sub> =5.5V, SHDN=0V or 6V | 0.01         |      | μA                   |                      |

| Thermal Shutdown            | Shutdown Temperature                 | 160          |      | $^{\circ}\mathbb{C}$ |                      |

| Thermal-Shutdown Hysteresis |                                      |              | 20   |                      | $^{\circ}\mathbb{C}$ |

# **Absolute Maximum Ratings**

| Supply Voltage                | 0.3V to 7.0V            |

|-------------------------------|-------------------------|

| Output Voltage                | 0.3V to $(V_{IN}+0.3V)$ |

| Output Short-Circuit Duration | Infinite                |

| Junction Temperature Range    | +150°C                  |

| Storage Temperature Range     | 65°C to +150°C          |

| Lead Temperature              | +250°C                  |

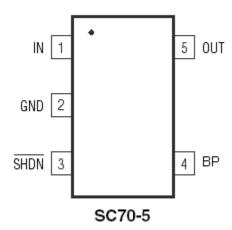

# **PIN CONFIGURATION**

TOP VIEW

# **PIN DESCRIPTION**

Table 2

| Pin | Name | Description                                                                                                                                             |  |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | IN   | Unregulated Input Supply.                                                                                                                               |  |

| 2   | GND  | Ground pin.                                                                                                                                             |  |

| 3   | EN   | Pull high to enable the regulator.                                                                                                                      |  |

| 4   | BP   | No external connection needed for normal operation.  Noise Bypass for Ultra-Low-Noise Operation by connecting a 10nF-30nF capacitor from Bypass to GND. |  |

| 5   | OUT  | Regulated Output Voltage. Bypass with a capacitor to GND.                                                                                               |  |

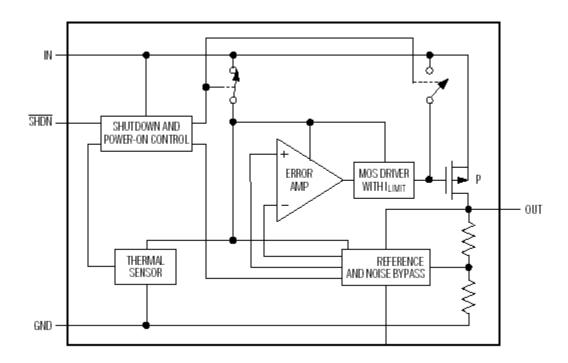

## **FUNCTIONAL BLOCK DIAGRAM**

## **FUNCTIONAL DESCRIPTIONS**

The ASI3101 is a low-noise, low-quiescent current, low-dropout linear regulator. It is supplied in a SC-70 package for space-restricted applications. These devices can supply loads up to 100mA. As shown in the *Functional Block Diagram*, the ASI3101 consists of a reference and noise bypass circuit, error amplifier, output drive transistor, internal feedback voltage-divider, thermal sensor, and maximum current limiter.

The internal reference is connected to the error amplifier's inverting input. The error amplifier compares this reference with the feedback voltage and amplifies the difference.

If the feedback voltage is lower than the reference voltage, the pass-transistor gate is pulled low. This allows more current to pass to the output and increases the output voltage. If the feedback voltage is too high, the pass transistor gate is pulled high, allowing less current to pass to the output. The parts are available with preset output voltages ranging from 1.8V to 3.3V in 100mV increments.

## **Stability**

The ASI3101 is a high performance LDO with emphasis in stability with low output capacitance. An output capacitor as low as 0.47uF is sufficient to maintain stability. The output capacitor can be increased to optimize performance. The ASI3101 will remain stable and in regulation with no load unlike many other voltage regulators. This is especially important in CMOS RAM-base keep-alive applications.

#### Internal P-Channel Pass Transistor

The ASI3101 feature a low impedance P-channel MOSFET pass transistor. This provides several advantages over similar designs using a PNP pass transistor, including low operating power and longer battery life. The ASI3101 consume only 90µA of quiescent current under most conditions.

## Output Short-Circuit Current Limit

The ASI3101 include a current limiter, which monitors and controls the pass transistor's gate voltage, limiting the output current to 150mA approximately, for example, in a short-circuit output situation.

#### Shutdown

The ASI3101 also features a low-power active shutdown mode. It has an N-channel MOSFET that turn off the device when it is disabled. This allows the output capacitor and load to discharge, de-energizing the load. In the shut down mode, the internal functional blocks such as voltage reference and error amplifier are turned off completely, and the quiescent current is less than  $1\mu A$ .

#### Thermal Protection Shutdown

The thermal protection shutdown feature protects the device from operating in over temperature condition. When the junction temperature exceeds +160°C, the thermal sensor signals the shutdown logic, turning off the pass transistor and allowing the IC to cool down. The thermal sensor turns the pass transistor on again after the IC's junction temperature drops by 20°C.

## Soft-Start Circuitry

The ASI3101 includes a soft-start circuitry to limit inrush current at turn-on. During power up, the output capacitor and output load are charged with a reduced output current. Shortly after the initial power up, the soft-start feature is terminated and normal operation is resumed.

#### Enable/Shutdown

The ASI3101 comes with an active-high enable pin that allows the regulator to be disabled. Forcing the enable pin low disables the regulator and puts it into the shutdown mode. Forcing the pin high enables the LDO. This pin cannot be left floating; as it may cause an undetermined state.

## Input/Output Capacitor

Use a 0.47µF capacitor on the ASI3101 input and a 0.47µF capacitor on the output, for high regulation performance. Larger input capacitor values and lower ESRs provide better noise rejection and line-transient response. Reduce output noise and improve load-transient response, stability, and power-supply rejection by using large output capacitors. Low ESR ceramic capacitors provide optimal performance at a minimum of space.

**Power Supply Rejection and Transient Response**The PSRR and transient response can be improved by increasing the values of the input and output bypass capacitors, and through passive filtering techniques.

## APPLICATION INFORMATION